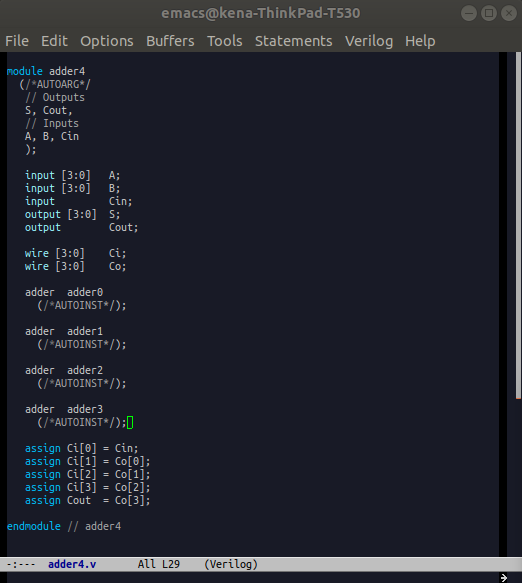

emacs verilog-mode/*AUTOINST*/下位階層のモジュールをインスタンスを記述するのって、面倒ですよね。verilog-mode には、そんな面倒を手助けしてくれる機能があります。 キーワードとして verilog-mode はカレント・ディレクトリからモジュール名 (この例では adder) と同じファイル名 (この例では adder.v) を探し、そのファイルから input, output, inout を読み取ります。もし、そのファイル(この例では adder.v)がカレント・ディレクトリにない場合は、シンボリック・リンクで対応して下さい。

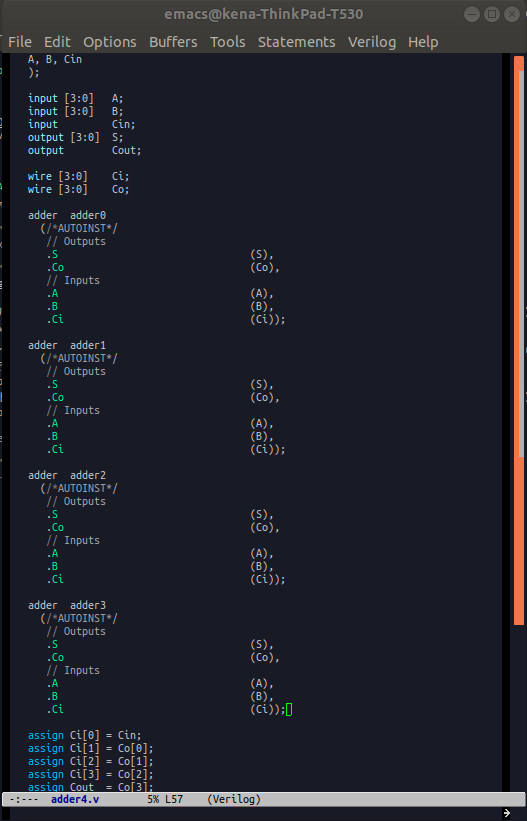

これで、自動コマンドとして、 上の例の場合、上位階層の信号名を指定していないため、インスタンスされる側の下位階層の input, output, inout の端子名が上位階層の信号名として使われます。 上位階層の信号名を指定する場合は、次に説明する

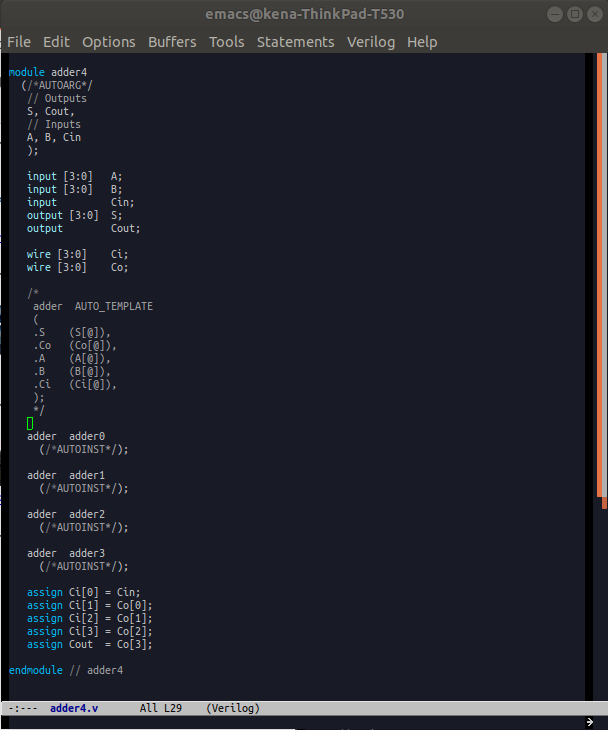

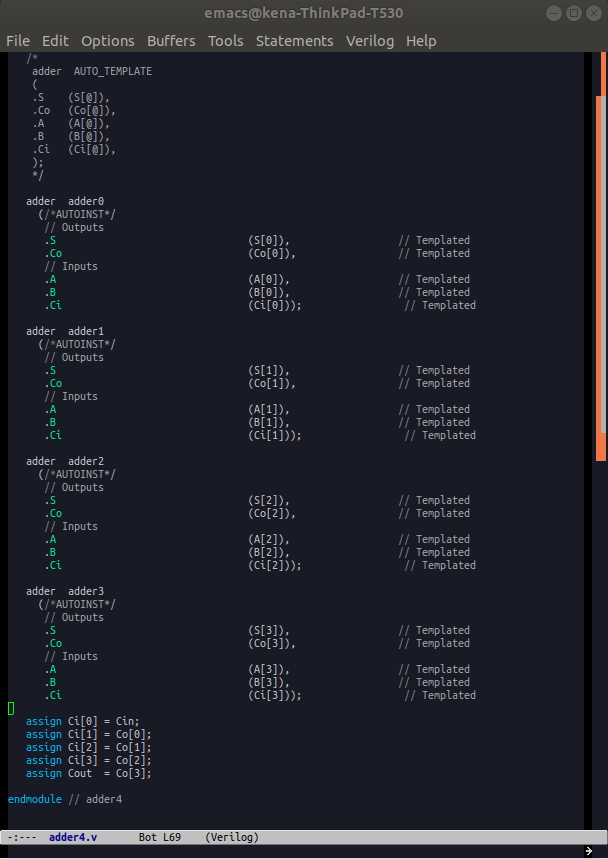

さらに上位階層の信号名の指定の中に@を入れると、@はインスタンス名の中に最初に出てくる数字と置き換えてくれます。

これで、自動コマンドとして、 如何ですか? このテクニックを知っていれば、何かと便利かと思います。

より詳しい AUTO_TEMPLATE の使い方はこちら → How do I use AUTO_TEMPLATE オンラインブートキャンプ無料説明会 |

自己紹介 50才になる半導体エンジニアです。大学で電子電気工学を学び、1990年にその分野のまま就職。ASICやマイコンの設計を長く続けてきましたが20年も同じ分野にいると業態も衰退したり変化するもので退職し、今は外資のIT系会社に再就職して設計請負業をやっております。 お問い合わせは nakata.xianzhi@outlook.com Linux と 小ネタ デジタル回路設計 海外駐在後記

|