モジュールの接続 ~ 概要 ~

Verilog−HDL では名前によるポート接続と順番によるポート接続の2種類がありました。 SystemVerilog では新たに .name と .* の2種類のポート接続が追加されました。

.name によるtポート接続

.name は名前によるポート接続をより簡単化したものです。 モジュール接続の記述において、ポート名とネット名が同一であるケースが非常に多く見受けられます。 .name を使うと、ポート名とネット名が同一である場合はポート名を記述すればよく、接続するネット名を省略できます。

なお、ポート名とネット名が一致しない信号については、名前によるポート接続と組み合わせて記述することができます。

| Verilog-HDL 名前によるポート接続 |

SystemVerilog .name によるポート接続 |

CNT6 CNT6 (

.CLK ( CLOCK ),

.RST_X ( RST_X ),

.CNT_EN ( CNT_EN ),

.CNTOUT ( CNTOUT )

);

|

CNT6 CNT6 (

.CLK ( CLOCK ),

.RST_X,

.CNT_EN,

.CNTOUT

);

|

.* によるポート接続

.* は .name をさらに簡単にしたものです。 ポート名とネット名が同一である場合、ポート名も省略して .* のみを記述します。 ポート名とネット名が異なる場合は、 .nameと同じように名前によるポート接続と組み合わせて記述することができます。

CNT6 CNT6 (

.*,

.CLK ( CLOCK ),

);

interface

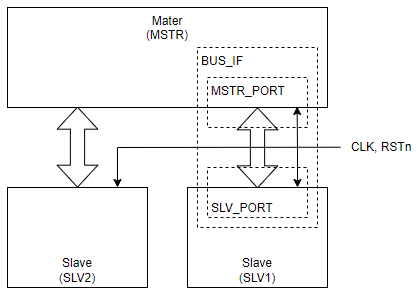

SystemVerilog では、新たに interface という概念が取り入れられました。モジュール間で共通の信号を interface で記述して呼び出すことで簡素化され、修正も楽になります。

BUS_IF.sv

interface #(parameter width=32) BUS_IF (input logic CLK, RST_X);

logic [7:0] ADDR;

logic WRITE;

logic ENABLE;

logic [width-1:0] WDATA;

logic [width-1:0] RDATA;

logic READY;

modport MSTR_PORT ( output ADDR, WRITE, ENABLE, WDATA, input RDATA, READY);

modport SLV_PORT ( input CLK, RST_X, input ADDR, WRITE, ENABLE, WDATA, output RDATA, READY);

endinterface

TOP.sv

module TOP (input logic CLK, RST_X, logic [7:0] CFG, output logic [3:0] FLAG);

BUS_IF #(32) BUS1(.CLK, .RST_X);

BUS_IF #(16) BUS2(.CLK, .RST_X);

Master MSTR( .CLK, .RST_X, .CFG, .FLAG, .BUS1(BUS1.MSTR_PORT), .BUS2(BUS2.MSTR_PORT) ) ;

Slave SLV1( .BUS(BUS1.SLV_PORT) ) ;

Slave SLV2( .BUS(BUS2.SLV_PORT) ) ;

endmodule

Master.sv

module Master (

input logic CLK, RST_X,

input logic [7:0] CFG,

output logic [3:0] FLAG,

BUS_IF.MSTR_PORT BUS1,

BUS_IF.MSTR_PORT BUS2

);

assign BUS1.ADDR = ...

assign BUS1.WRITE = ...

assign BUS1.ENABLE = ...

assign BUS1.WDATA = ...

assign BUS2.ADDR = ...

assign BUS2.WRITE = ...

assign BUS2.ENABLE = ...

assign BUS2.WDATA = ...

Slave.sv

module Slave (

BUS_IF.SLV_PORT BUS

);

Slave_sub sub(.BUS);

Slave_sub.sv

module Slave_sub (

BUS_IF.SLV_PORT BUS

);

assign BUS.RDATA = ...

assign BUS.READY = ...

|